Phoenip Technical Reference Series

# System BIOS for IBM® PC/XT<sup>™</sup>/AT® Computers and Compatibles

The Complete Guide to ROM-Based System Software

**Phoenix Technologies Ltd.**

Phoenip Technical Reference Series

System BIOS for IBM®PC/XT™/AT® Computers and Compatibles

The Complete Guide to ROM-Based System Software

Phoenix Technologies Ltd.

# •••

Addison-Wesley Publishing Company, Inc. Reading, Massachusetts Menlo Park, California New York Don Mills, Ontario Wokingham, England Amsterdam Bonn Sydney Singapore Tokyo Madrid San Juan Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial capital letters.

#### Limitation of Liability

While every reasonable precaution has been taken in the preparation of this book, the author and the publishers assume no responsibility for errors or omissions, or for the uses made of the material contained herein or the decisions based on such use. No warranties are made, express or implied, with regard to the contents of this work, its merchantability, or fitness for a particular purpose. Neither the author nor the publishers shall be liable for direct, special, incidental, or consequential damages arising out of the use or inability to use the contents of this book.

### Library of Congress Cataloging-In-Publication Data

System BIOS for IBM PC/XT/AT computers and compatibles / Phoenix Technologies, Ltd. p. cm. -- (Phoenix technical reference series) ISBN 0-201-51806-6 : 1. IBM Personal Computer. 2. IBM Personal Computer XT. 3. IBM Personal Computer AT. 4. Operating systems (Computers) I. Phoenix Technologies. II. Title: BIOS. III. Series. QA76.8.I2594S97 1989 004.4'469--dc20 89-17557 CIP

Copyright © 1989, 1988, 1987 by Phoenix Technologies Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

Cover design by Hannus Design Associates Text design by Phoenix Technologies Ltd. Set in 10-point Modern by Phoenix Technologies Ltd.

ISBN: 0-201-51806-6 EFGHIJ-AL-93210 Fifth Printing, August 1990

### Trademarks

This manual acknowledges the following trademarks:

Ashton-Tate and Framework are registered trademarks of Ashton-Tate Corporation.

AST is a registered trademark of AST Research, Inc.

AT, IBM, Personal Systems/2, PS/2, and PC/AT are registered trademarks of the International Business Machines Corporation. PC-DOS, PC/XT, VGA, CGA, MCA, MDA, EGA, OS/2, and Micro Channel are trademarks of the International Business Machines Corporation.

Hercules, Hercules Graphic Card, and Hercules Graphic Adapter are trademarks of Hercules Computer Technology.

Intel is a registered trademark of Intel Corporation.

1-2-3, Lotus, and Symphony are registered trademarks of Lotus Development Corp.

Motorola is a registered trademark of Motorola Semiconductor Products, Inc.

MS, MS-DOS, XENIX, and Microsoft are registered trademarks of Microsoft Corporation.

NEC and Multisync are registered trademarks of Nippon Electric Corporation.

Quadram is a registered trademark of Quadram Corporation.

### Dedication

To the IBM engineers and programmers who designed and coded the IBM PC, XT, and AT BIOSs.

# **Table of Contents**

| Foreword                   | xvii  |

|----------------------------|-------|

| About This Book            | xxiii |

| Acronyms and Abbreviations | xxvii |

# Chapter 1 — The ROM BIOS

| Overview                                 |                 | <br> | 1  |

|------------------------------------------|-----------------|------|----|

| BIOS: Theory of Operation                |                 | <br> | 4  |

| BIOS Memory Usage                        |                 | <br> | 8  |

| Interrupt Vector Table                   |                 | <br> |    |

| Unexpected Interrupt Handler             |                 | <br> | 12 |

| System BIOS Functions and BIOS Diversity | • • • • • • • • | <br> | 14 |

| Video BIOS Functions and BIOS Diversity  |                 | <br> | 16 |

| Summary: The BIOS Services               |                 | <br> | 18 |

# Chapter 2 — System RAM Data

| Overview                                              |

|-------------------------------------------------------|

| Interrupt Vectors                                     |

| BIOS Data Area                                        |

| Power-On Self Test Definitions                        |

| INT 10h Video Service Data Definitions 39             |

| INT 11h Equipment List Service Data Definitions       |

| INT 12h Memory Size Service Data Definition41         |

| INT 13h Diskette Service Data Definitions 42          |

| INT 14h Serial Communication Service Data Definitions |

| INT 16h Keyboard Data Service Definitions and         |

| INT 09h Keyboard Service Interrupt Data Definitions   |

| INT 17h Parallel Printer Service Data Definitions     |

| INT 19h Bootstrap Loader Service Data Definitions     |

| INT 1Ah Time-of-Day Service Data Definitions          |

|                                                       |

# Chapter 3 — CMOS RAM Data

| Overview           | 49 |

|--------------------|----|

| CMOS RAM I/O Ports | 50 |

| Accessing CMOS RAM | 51 |

| CMOS RAM Data      | 52 |

# Chapter 4 — ROM BIOS Data

| Overview                                  | 57 |

|-------------------------------------------|----|

| ROM Address Compatibility Table           | 58 |

| System Configuration Data Table (AT only) | 60 |

| Diskette Parameter Table                  | 61 |

| AT Fixed Disk Parameter Table             | 63 |

| XT Fixed Disk Parameter Table             | 68 |

| Baud Rate Initialization                  | 70 |

# Chapter 5 – I/O Port Addresses

| Overview               |    | 71 |

|------------------------|----|----|

| Hardware I/O Port List |    | 72 |

| Video I/O Port List    | •• | 94 |

# Chapter 6 — Power-On Self Tests (POST)

| Overview                                         | 103 |

|--------------------------------------------------|-----|

| POST Procedures                                  | 105 |

| Rules for Positioning I/O Expansion ROM          | 107 |

| Re-Entering Real Mode (80286-based systems only) | 109 |

| INT 19h, INT 18h, and System Boot                | 110 |

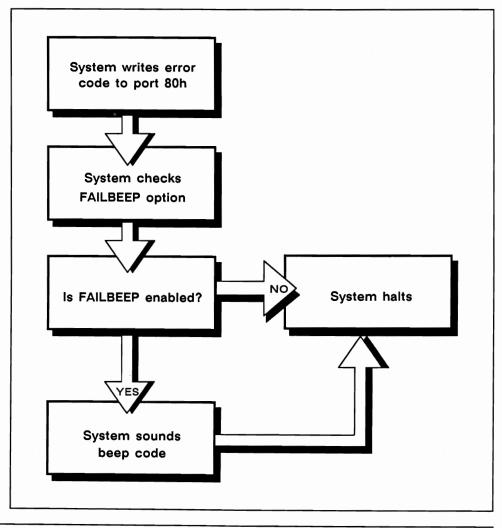

| POST Error Handling in AT Systems                | 111 |

| POST Error Handling in XT Systems                | 111 |

|                                                  |     |

# Chapter 7 — INT 02h Nonmaskable Interrupt

| Overview                                   | 113 |

|--------------------------------------------|-----|

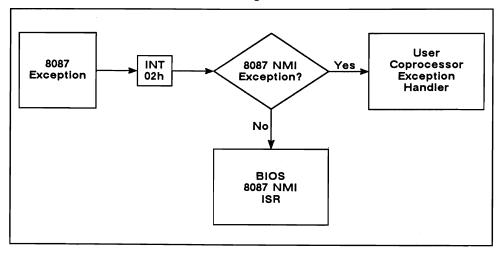

| XT NMI Handling                            | 115 |

| 3087 Coprocessor Exceptions                | 116 |

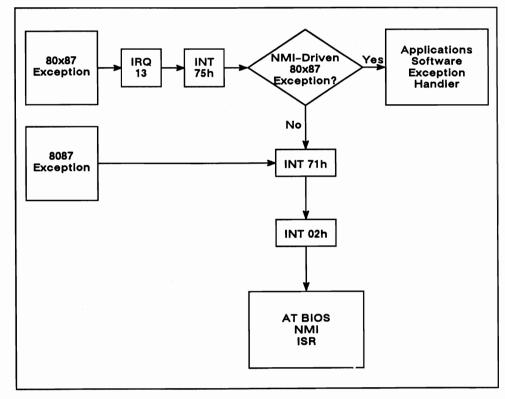

| AT NMI Handling                            | 117 |

| 80x87 Coprocessor Exceptions in AT Systems | 119 |

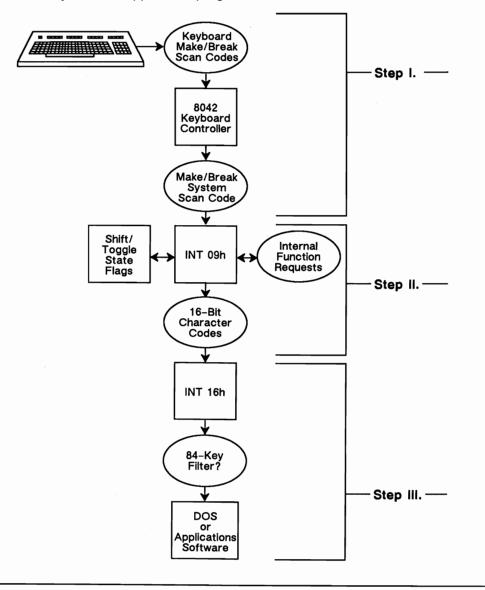

# Chapter 8 - INT 09h and INT 16h Keyboard Services

| Overview                                                                                   |

|--------------------------------------------------------------------------------------------|

| Theory of Operation                                                                        |

| Keyboard I/O Ports                                                                         |

| System RAM Data                                                                            |

| INT 09h: Internal Function Requests                                                        |

| INT 09h: System Reset ( <ctrl> <alt> <del>)</del></alt></ctrl>                             |

| INT 09h: Break ( <ctrl> <break> or <ctrl> <scroll lock="">)</scroll></ctrl></break></ctrl> |

| INT 09h: Pause ( <ctrl> <num lock="">)</num></ctrl>                                        |

| INT 09h: Print Screen ( <prtsc> or <shift> <prtsc>)</prtsc></shift></prtsc>                |

| INT 09h: System Request ( <sysreq>)137</sysreq>                                            |

| INT 16h: Keyboard DSR                                                                      |

| INT 16h: AH = 00h Read Keyboard Input                                                      |

| INT 16h: AH = 01h Return Keyboard Status141                                                |

| INT 16h: AH = 02h Return Shift Flag Status 142                                             |

| INT 16h: AH = 03h Set Typematic Rate and Delay143                                          |

| INT 16h: AH = 05h Store Key Data 144                                                       |

| INT 16h: AH = 10h Read Extended Keyboard Input 145                                         |

| INT 16h: AH = 11h Return Extended Keyboard Status                                          |

| INT 16h: AH = 12h Return Extended Shift Flags Status                                       |

| How to Read Character Code Tables 149                                                      |

| Character Codes: AH = 00h/01h 151                                                          |

| Character Codes: AH = 10h/11h 156                                                          |

|                                                                                            |

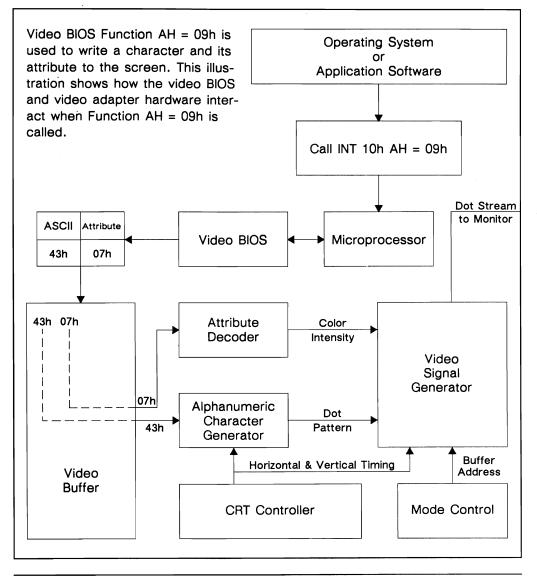

# Chapter 9 - INT 10h Video Service

| Overview                 | 161 |

|--------------------------|-----|

| Theory of Operation      | 164 |

| MDA Hardware Environment | 174 |

# Chapter 9 - INT 10h Video Service, Continued

| CGA Hardware Environment                                                                 |

|------------------------------------------------------------------------------------------|

| VGA Hardware Environment                                                                 |

| Video Modes                                                                              |

| System RAM Data                                                                          |

| Summary of INT 10h Functions                                                             |

| How Functions Are Called                                                                 |

| Error Handling                                                                           |

| Function: AH = 00h Set Video Mode                                                        |

| Function: AH = 01h Set Text Mode Cursor Size                                             |

| Function: AH = 02h Set Cursor Position                                                   |

| Function: AH = 03h Read Current Cursor Position                                          |

| Function: AH = 04h Read Light Pen Position                                               |

| Function: AH = 05h Select New Video Page                                                 |

| Function: AH = 06h Scroll Current Page Up<br>Function: AH = 07h Scroll Current Page Down |

| Function: AH = 08h Read Character/Attribute from Screen                                  |

| Function: AH = 09h Write Character/Attribute to Screen                                   |

| Function: AH = 0Ah Write Character Only to Screen                                        |

| Function: AH = 0Bh Set Color Palette                                                     |

| Function: AH = 0Ch Write Pixel                                                           |

| Function: AH = 0Dh Read Pixel                                                            |

| Function: AH = 0Eh Write Teletype to Active Page                                         |

| Function: AH = 0Fh Return Video Status                                                   |

| Function: AH = 10h Set Palette/Color Registers                                           |

| Function: AH = 11h Load Character Generator                                              |

| Function: AH = 12h Alternate Select                                                      |

| Function: AH = 13h Write String                                                          |

| Function: AH = 1Ah Read/Write Display Combination Code                                   |

| Function: AH = 1Bh Return Functionality/State Information                                |

| Function: AH = 1Ch Save/Restore Video State                                              |

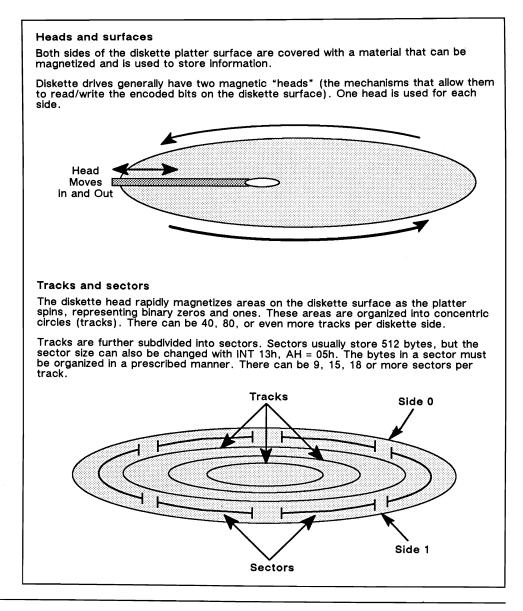

# Chapter 10 - INT 13h Diskette Service

| Overview             | 263 |

|----------------------|-----|

| Summary of Functions | 265 |

| Theory of Operations | 266 |

# Chapter 10 - INT 13h Diskette Service, Continued

| Hardware Environment                         |

|----------------------------------------------|

| System RAM Data                              |

| CMOS RAM Data                                |

| ROM BIOS Data                                |

| Diskette Service I/O Ports                   |

| Error Handling                               |

| Function: AH = 00h Reset Diskette System     |

| Function: AH = 01h Read Diskette Status      |

| Function: AH = 02h Read Diskette Sectors     |

| Function: AH = 03h Write Diskette Sectors    |

| Function: AH = 04h Verify Diskette Sectors   |

| Function: AH = 05h Format Diskette Track     |

| Function: AH = 08h Read Drive Parameters 293 |

| Function: AH = 15h Read Drive Type 295       |

| Function: AH = 16h Detect Media Change 296   |

| Function: AH = 17h Set Diskette Type 297     |

| Function: AH = 18h Set Media Type for Format |

| INT 0Eh Diskette Hardware Interrupt 300      |

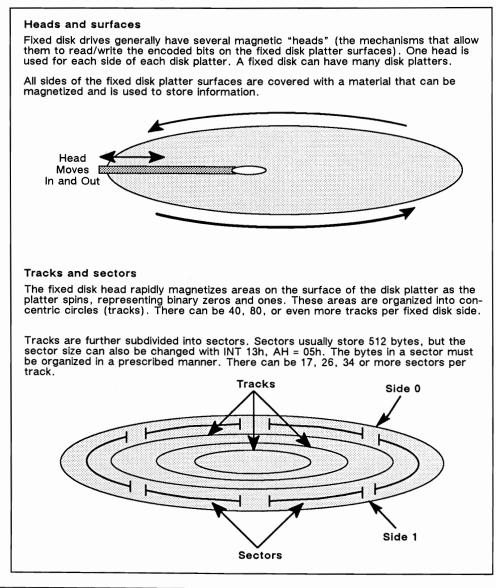

# Chapter 11 - INT 13h Fixed Disk Service

| Overview                                            |

|-----------------------------------------------------|

| Fixed Disk Service Function Summary                 |

| Theory of Operations                                |

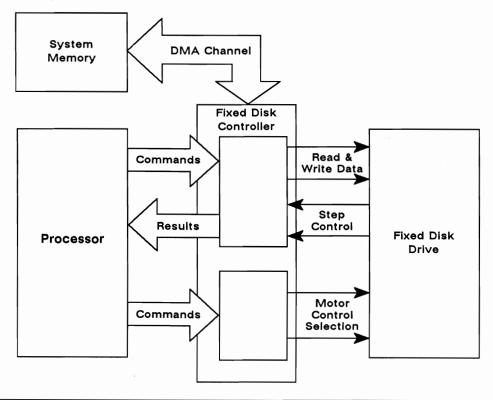

| Hardware Environment                                |

| System RAM Data                                     |

| CMOS RAM Data                                       |

| ROM BIOS Data                                       |

| Fixed Disk Service I/O Ports 322                    |

| Error Handling                                      |

| Function: AH = 00h Reset Diskette(s) and Fixed Disk |

| Function: AH = 01h Read Fixed Disk Status           |

| Function: AH = 02h Read Sectors 329                 |

| Function: AH = 03h Write Sectors                    |

| Function: AH = 04h Verify Sectors                   |

| Function: AH = 05h Format Cylinder                  |

| Function: AH = 06h Format Bad Track                 |

# Chapter 11 - INT 13h Fixed Disk Service, Continued

| Function: | AH = 07h | Format Drive                         |

|-----------|----------|--------------------------------------|

|           |          | Read Drive Parameters                |

|           |          | Initialize Drive Parameters          |

|           |          | Read Long Sectors                    |

| Function: | AH = OBh | Write Long Sectors                   |

|           |          | Seek to Cylinder                     |

| Function: | AH = 0Dh | Alternate Fixed Disk Reset           |

| Function: | AH = 0Eh | Diagnostics 1: Read Test Buffer 347  |

| Function: | AH = 0Fh | Diagnostics 2: Write Test Buffer 348 |

| Function: | AH = 10h | Test for Drive Ready                 |

| Function: | AH = 11h | Recalibrate Drive                    |

| Function: | AH = 12h | Controller RAM Diagnostic            |

| Function: | AH = 13h | Controller Drive Diagnostic          |

| Function: | AH = 14h | Controller Internal Diagnostic 353   |

| Function: | AH = 15h | Read Fixed Disk Type 354             |

# Chapter 12 — INT 14h Serial Communications Service

| Overview                                                 |

|----------------------------------------------------------|

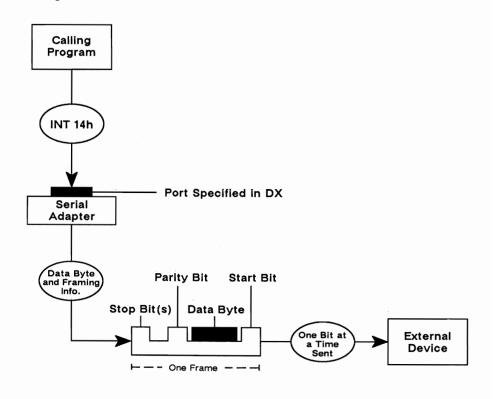

| Theory of Operation                                      |

| System RAM Data                                          |

| ROM BIOS Data                                            |

| Serial Communications I/O Ports                          |

| Error Conditions                                         |

| Function: AH = 00h Initialize Serial Communications Port |

| Function: AH = 01h Send Character                        |

| Function: AH = 02h Receive Character 377                 |

| Function: AH = 03h Read Serial Port Status               |

# Chapter 13 — INT 15h System Services

| Overview             |

|----------------------|

| Summary of Functions |

| Hardware Environment |

| System RAM Data      |

| CMOS RAM Data        |

| ROM BIOS Data                                             |

|-----------------------------------------------------------|

| System Services I/O Ports                                 |

| Function: AH = 00h Turn Cassette Motor On                 |

| Function: AH = 01h Turn Cassette Motor Off                |

| Function: AH = 02h Read Cassette                          |

| Function: AH = 03h Write to Cassette                      |

| Function: AH = 4Fh Keyboard Intercept                     |

| Function: AH = 80h Device Open                            |

| Function: AH = 81h Device Close                           |

| Function: AH = 82h Program Termination                    |

| Function: AH = 83h Set Event Wait Interval                |

| Function: AH = 84h Joystick Support 400                   |

| Function: AH = 85h System Request Key 402                 |

| Function: AH = 86h Wait                                   |

| Function: AH = 87h Move Block 404                         |

| Function: AH = 88h Read Extended Memory Size 408          |

| Function: AH = 89h Switch Processor to Protected Mode     |

| Function: AH = 90h Device Busy 411                        |

| Function: AH = 91h Interrupt Complete                     |

| Function: AH = C0h Return System Configuration Parameters |

# Chapter 14 — INT 17h Parallel Printer Service

| Overview                                   | ; |

|--------------------------------------------|---|

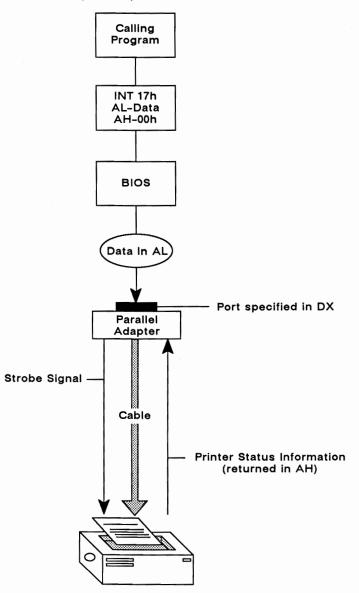

| Theory of Operation                        | , |

| System RAM Data                            |   |

| Parallel Printer I/O Ports                 | 2 |

| Error Handling                             | 3 |

| Function: AH = 00h Print Character         | ļ |

| Function: AH = 01h Initialize Printer 425  | 5 |

| Function: AH = 02h Read Printer Status 426 | ; |

# Chapter 15 — INT 1Ah Time-of-Day Service

| erview             | 27 |

|--------------------|----|

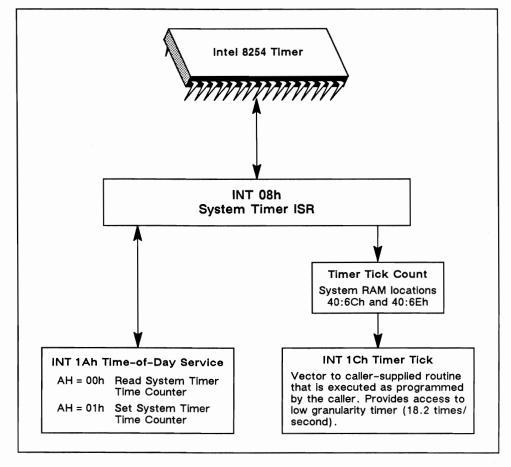

| eory of Operations | 30 |

# Chapter 15 - INT 1Ah Time-of-Day Service, Continued

| System RAM Data                                   |

|---------------------------------------------------|

| CMOS RAM Data                                     |

| Time-of-Day Service I/O Ports                     |

| Error Handling                                    |

| Function: AH = 00h Read System Timer Time Counter |

| Function: AH = 01h Set System Timer Time Counter  |

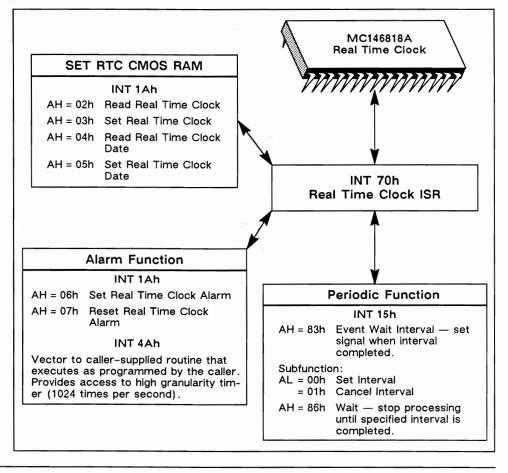

| Function: AH = 02h Read Real Time Clock Time      |

| Function: AH = 03h Set Real Time Clock Time       |

| Function: AH = 04h Read Real Time Clock Date      |

| Function: AH = 05h Set Real Time Clock Date       |

| Function: AH = 06h Set Real Time Clock Alarm      |

| Function: AH = 07h Reset Real Time Clock Alarm    |

| Function: AH = 80h Set Sound Source               |

| INT 08h System Timer ISR 446                      |

| INT 70h Real Time Clock ISR 449                   |

| INT 1Ch Timer Tick ISR 452                        |

| INT 4Ah Alarm ISR                                 |

# Chapter 16 — Single Function BIOS Services

| Ove | rviev | v                           | 3 |

|-----|-------|-----------------------------|---|

| INT | 05h   | Print Screen Service        | 5 |

| INT | 11h   | Equipment List Service      | 7 |

| INT | 12h   | Memory Size Service         | 8 |

| INT | 19h   | Bootstrap Loader Service 45 | 9 |

# Appendix A — AT BIOS Error Codes and Messages

| Introduction                         | 163 |

|--------------------------------------|-----|

| BM BIOS POST and Boot Messages       | 164 |

| Phoenix BIOS POST and Boot Messages4 | 166 |

| Phoenix BIOS Run-Time Messages4      | 170 |

| Phoenix BIOS Beep Codes4             | 471 |

| SETUP Messages                       | 177 |

# Appendix B — XT BIOS Error Messages

| Introduction                                                            |       |                               |     |

|-------------------------------------------------------------------------|-------|-------------------------------|-----|

| Phoenix XT BIOS POST and Boot Mess<br>Phoenix XT BIOS Run-Time Messages | •     |                               |     |

| Glossary                                                                |       |                               |     |

| Additional Resources                                                    |       |                               |     |

| Index                                                                   | ••••• | • • • • • • • • • • • • • • • | 495 |

# Foreword

### The Micro Revolution

The personal computer has come a long way from being a hacker's hobby in basements and garages to a multibillion-dollar industry. In the early days, programming carried with it an aura of history-in-the-making, of a revolution that would alter not only the business world, but the fabric of society as well. In the personal computer, we had found a new vehicle for the exchange of ideas and the formation of a global village. Personal computing promised to democratize technology.

At that time, the structure of computing environments centered around the mainframe. Mainframes cost millions of dollars, filled up large air-conditioned rooms and required a host of programmers to appease and maintain them. Users who wished to supplicate the mainframe for a specific task were forced to request an audience through their Management Information Systems group. They then had to wait months and even years for their applications to be built and run, often sacrificing precious time and frustrating their creative spirits.

I was an undergraduate at M.I.T. when I first heard of the microprocessor. It was the key to the computer kingdom that all hackers dreamt about, a way to bring computing power to individuals without the intervention of bureaucracies. The microprocessor created a cult following among programmers.

In the mid-seventies, large computer companies, built around the proprietary technology of their mainframes and minicomputers, downplayed the micro's potential. As often happens in the business world, it took a group of vision-aries and entrepreneurs to capitalize on that potential and to create an in-dustry around it.

Once the market had been formed, though, the computer establishment realized there was gold in those silicon hills and valleys and rushed to enter. It was actually just what the fledgling industry needed: someone with the marketing clout to establish a standard platform. One cannot advance technology without a platform to serve as a basis for expansion and evolution into higher forms.

Thus, the IBM PC was born, and with it the era of DOS.

### **BIOS: The Missing Link**

I founded Phoenix in 1979 as a supplier of programmers' tools to support the DOS standard. We were successful, but not a phenomenon until we broke through with the PC ROM BIOS in May 1984. It proved to be the missing link for manufacturers to build systems that were 100 percent compatible with the IBM PC and, just as important, 100 percent legal.

Our "clean room" methodology was responsible. "Contaminated" engineers studied the BIOS' functionality and passed on those functions to "virgin" engineers, who had never seen the BIOS and who then wrote the code that would accomplish specific tasks. I am proud to say the Phoenix ROM BIOS was one of the keys that unlocked the PC market and enabled it to grow to its present proportions.

Phoenix was your archetypal start-up. The first bus architecture that Phoenix supported was the VW platform as it was driven from one programmer's garage to another's basement, picking up products and orders for our initial line of programmers' tools. Our corporate meeting room was in a basement. I would lead visiting computer executives down a narrow stairwell to a dark basement, where they would share an old sofa with a bunch of cats, shedding hairs all over their pinstriped suits. That was three office buildings ago, and we're still growing.

Over 300 companies have licensed our ROM BIOS. Today, there are more installed Phoenix BIOSs than IBM's, with over 14 million systems booting up with the Phoenix name as the first item to appear on screen.

Our engineering ventures did not end with the BIOS. Since the PC standard is always changing, compatibility is a moving target. In fact, the BIOS has been an evolving piece of indispensable code which has been continually upgraded to maintain a system's compatibility with the advancements of the PC's capabilities.

Phoenix also helped to pioneer emulation technologies that enable technical and graphical workstations to become DOS compatible. Our software coprocessor technology is one of the key reasons UNIX workstations are currently enjoying their acceptance in mainstream computing environments. Our latest product development, PhoenixPage, is a systems software suite that supports printer standards, such as PostScript-language compatibility.

### Portrait of a Company as a Young BIOS

Phoenix is in the middle of the micro madness, but with a method. Phoenix's strategy is based on the revolution at the heart of the computer industry's dynamic growth. The emergence of open standards has drastically altered the way we do business with advanced technologies. Contrary to the conventional wisdom that looked for a market edge through the development of proprietary technologies, companies are realizing that industry-wide adoption of standards is a prerequisite for growth, both in technical and financial terms.

The diversification of the Phoenix product line revolves around a central concept: the promulgation of open standards. In the current proliferation of operating systems, CPUs, chip sets, system board configurations, and bus architectures, Phoenix's flexible systems software gives a manufacturer freedom of design and end users the assurance of quality compatibility.

The BIOS itself may serve as a perfect business model in understanding Phoenix's role in the microcomputer revolution. Just like systems-level components in the architecture of a computer, there are players in the computer industry that are mainly invisible to end users, but who possess roles that are crucial to the smooth execution of product cycles and advancing technologies.

Just as the BIOS sits at the heart of the PC, where software meets hardware, and interfaces communications between the operating system, CPU, and a computer's peripheral devices (monitor, printer, disk drives, etc.), so Phoenix is positioned at the center of the PC universe, working closely with semiconductor, hardware, and peripheral manufacturers; operating system and independent software developers; and system integrators, ensuring compatible designs among them all, peace of mind for purchasers and end users, and a stable and open platform for programmers.

### PC Compatibility: The Only Game in Town

The PC standard is now entirely software-driven. It is not dependent on IBM's hardware architecture. The goal of a standard is not IBM hardware emulation, but a hardware-independent compatibility based on the ability to run PC applications. It was as much to achieve compatibility with each other as with IBM that caused most of the industry's largest manufacturers (some of whom once shunned PC compatibility) to jump on the bandwagon.

The value of compatibility with the PC standard from the end user's viewpoint is that it offers investment protection, portability, and access to the world's largest library of applications software packages. These considerations have made 100 percent compatibility the main customer-driven demand in the personal computer marketplace.

In the past few years, the PC industry has seen phenomenal growth. Now that the standard has been established, the platform is in place to launch an even more impressive and expansive future. The goal for software developers is to break away from hardware-imposed stagnation and push the PC environment to new heights. Phoenix's biggest challenge as a company will be to help manufacturers and software developers integrate compatibility into new products with smart, innovative engineering.

### Open Sesame

Standards advance technology. The establishment of a common platform enables hardware and software developers to evolve more advanced technologies, since they now have a target and a customer base to make it worthwhile. The adoption of standards frees engineering resources to concentrate on differentiating products with expanded capabilities.

Phoenix's goal has always been to support standards in the micro environment. Open standards enable an industry to reap the rewards of advanced technology by attracting the widest possible customer base and applications. Phoenix provides a cost-effective engineering resource to solve the integration challenges the PC industry faces.

We are offering this series of BIOS technical references in the same spirit of "openness" that has characterized our research and development, from the days of our programmers' tools through the introduction of our PC BIOS and creation of the compatibles market.

Open systems need open communications. For personal computing to succeed in society, information must be readily available to allow individuals to exploit its capabilities. These manuals provide a complete and clear picture of the design of the PC standard. They describe the parameters of compatibility and how best to design a system based on the standard. Programmers will find a treasure trove between these covers. They will have easy access to the PC architecture and will have a secure and stable platform to which to write. My hope is that these manuals will help put the personal back into computing.

Neil J. Colvin

111.

Chairman Phoenix Technologies Ltd.

•

# **About This Book**

### What this book is about

System BIOS for IBM PC/XT/AT Computers and Compatibles is a detailed technical reference that describes the BIOS, the component of PC, XT, and AT systems that insulates both applications software and single-tasking operating systems, such as MS-DOS, from direct manipulation of PC hardware. The information provided in this book is applicable to all PC, XT, and AT computers and compatibles.

### Who should read this book

System BIOS for IBM PC/XT/AT Computers and Compatibles provides the most comprehensive source of information about IBM PC, XT, and AT and compatible BIOSs available today. It can be used by anyone interested in learning more about IBM or compatible computers.

Applications programmers and device driver developers will find a thorough discussion of each BIOS device service and function, including all levels of video BIOS, from MDA and CGA through EGA and VGA. In addition, *System BIOS for IBM PC/XT/AT Computers and Compatibles* defines, to the bit level, all IBM and compatible I/O port addresses and BIOS-related CMOS RAM and system RAM data.

Hardware technicians and other system troubleshooters will appreciate the complete list of all BIOS-generated error messages, their likely causes, and suggested solutions.

### Other volumes in this series

System BIOS for IBM PC/XT/AT Computers and Compatibles is one of several volumes about BIOS software in the Phoenix Technical Reference Series. Other volumes are:

ABIOS for IBM PS/2 Computers and Compatibles — a complete technical reference describing the portion of a PS/2 BIOS that supports multitasking operating systems such as OS/2.

CBIOS for IBM PS/2 Computers and Compatibles – a complete technical reference describing the portion of a PS/2 BIOS that supports single-tasking operating systems such as DOS.

The volumes of this series are a natural companion for anyone who owns and programs an IBM PC, XT, AT, or PS/2, or any compatible system.

### How to find information

System BIOS for IBM PC/XT/AT Computers and Compatibles is organized into several major parts. Chapter 1 provides a general summary of BIOS concepts. Chapters 2–6 describe BIOS and system data definitions and I/O port usage. Chapters 7–16 describe the individual BIOS services and serve as a technical reference. Appendixes A and B provide comprehensive lists of potential error messages for AT and XT-compatible systems.

Each service-specific chapter (7-16) is organized in the same way. There is a description of the service and the theory of operations for this service, a list of all I/O ports and data definitions accessed by the service, a discussion on how errors are handled for this service, and complete descriptions of each service function. The function descriptions include an explanation of what the function does, the function's required inputs and outputs, and any special programming considerations.

### A word about diversity

In the eight years since the original PC emerged, there have been countless manufacturers of PC, XT, and AT systems and BIOS products. Although all BIOSs in IBM-compatible microcomputers by definition have to be compatible with the IBM standard, there has been a good deal of diversity in the detail of BIOS architecture.

This diversity makes it difficult to precisely identify terms such as PC-, XT-, or AT-compatible. BIOS functions that appear only in IBM AT systems can be found in the Phoenix XT BIOS. And there are many different combinations of BIOS functions in various XT or AT clones. Whenever possible, we provide directions on how to find out if a particular function is supported.

### What we assume you know

This book assumes a basic knowledge of 8086, 80286, and 80386 assembly language programming concepts, PC architecture, and operating system concepts. If you are new to these subjects, you may want to refer to the introductory texts listed at the end of this book.

### Acknowledgments

First and foremost, we would like to acknowledge the vision and technical skill of Neil Colvin, founder, Chairman of the Board and Chief Technical Officer of Phoenix Technologies Ltd. We also acknowledge the expert guidance of Lance Hansche, President and CEO of Phoenix Technologies Ltd.

We especially want to acknowledge the contributions made by Jeff Bobzin, Dave Hirschman, and Bob Vandette — the Phoenix engineers who initially brought the BIOS to life, as well as the continuing efforts of Eric Enge, Paula Bishop, Jeff Kleiman, Debbie Schultz, Stan Lyness, Greg Honsa, Bruce Cairns, Ruth Brent, Jeff Wheeler, and the rest of the Phoenix staff, who keep the BIOS alive and compatible with the widest range of PC hardware.

This volume could not have been produced without the tireless efforts of Rich Levandov, Vice President of Marketing, and Henry Suwinsky, Project Manager.

We would like to thank Kathy Schiff, Manager of Technical Communications, who provided editorial guidance and direction in the production of this book and Jeff Evangelista, who contributed two well-written chapters. And last but not least, our special thanks goes to Sandie Zierak, Chief Production Coordinator, for her invaluable contributions in document design, graphics, and production.

The Authors

Mike Boston Paul Narushoff

Phoenix Technologies Ltd. Norwood, MA May, 1989 ·

# Acronyms and Abbreviations

| The following | abbreviations and acronyms are used in this manual:   |

|---------------|-------------------------------------------------------|

| ACK           | Acknowledge (keyboard and serial port commands)       |

| ACR           | Fixed disk adapter controller register                |

| ALE           | Address latch enable                                  |

| ANSI          | American National Standards organization              |

| ARB           | Access rights byte (part of 80286/80386 instruction)  |

| ASCII         | American Standard Code for Information Interchange    |

| ASIC          | Application-specific integrated circuit               |

| ASR           | Fixed disk adapter status register                    |

| АТ            | Advanced technology                                   |

| b             | Binary                                                |

| BAT           | Basic assurance test (keyboard diagnostic)            |

| BCD           | Binary coded decimal                                  |

| BIOS          | Basic input/output system                             |

| bps           | Bits per second                                       |

| CAS           | Column address strobe                                 |

| CCB           | Command control block                                 |

| CGA           | Color graphics adapter                                |

| CLK           | Clock line on a microprocessor                        |

| CMOS          | Complementary metal oxide semiconductor               |

| CRC           | Cyclic redundancy check                               |

| CSB           | Command specify block                                 |

| CTS           | Clear to send                                         |

| DAC           | Digital-to-analog converter                           |

| DCC           | Display combination code                              |

| DIN           | Deutsche Industrie Norm                               |

| DIP           | Dual inline package                                   |

| DMA           | Direct memory access                                  |

| DPL           | Descriptor privilege level - part of 80286/80386 code |

| DSR           | Data set ready                                        |

| DSR           | Device service routine                                |

| DTR           | Data terminal ready                                   |

| EA            | Effective address                                     |

|               |                                                       |

# Acronyms and Abbreviations, Continued

1

| ECCError checking and correctionEGAEnhanced graphics adapterEIAElectronic Industries AssociationEISAExtended industry standard architectureEOIEnd of interruptEPLExtended privilege levelEPROMErasable programmable read-only memoryESDIEnhanced small device interfaceETBEnd of transmission blockFCBFormat control block - disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulationMHzMegahertz | EBCDIC | Extended Binary Coded Decimal Interchange      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------|

| EIAElectronic Industries AssociationEISAExtended industry standard architectureEOIEnd of interruptEPLExtended privilege levelEPROMErasable programmable read-only memoryESDIEnhanced small device interfaceETBEnd of transmission blockFCBFormat control block — disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobits per secondLDTLocal descriptor table registerLDTLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                             | ECC    | Error checking and correction                  |

| EISAExtended industry standard architectureEOIEnd of interruptEPLExtended privilege levelEPROMErasable programmable read-only memoryESDIEnhanced small device interfaceETBEnd of transmission blockFCBFormat control block — disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt control wordINTInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor table registerLDDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                              | EGA    | Enhanced graphics adapter                      |

| EOIEnd of interruptEPLExtended privilege levelEPROMErasable programmable read-only memoryESDIEnhanced small device interfaceETBEnd of transmission blockFCBFormat control block - disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobits per secondLDTLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                   | EIA    | Electronic Industries Association              |

| EPLExtended privilege levelEPROMErasable programmable read-only memoryESDIEnhanced small device interfaceETBEnd of transmission blockFCBFormat control block — disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt control wordINTInterrupt request line or Interrupt requestIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                | EISA   | Extended industry standard architecture        |

| EPROMErasable programmable read-only memoryESDIEnhanced small device interfaceETBEnd of transmission blockFCBFormat control block — disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt control wordINTInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                             | EOI    | End of interrupt                               |

| ESDIEnhanced small device interfaceETBEnd of transmission blockFCBFormat control block – disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                | EPL    | Extended privilege level                       |

| ETBEnd of transmission blockFCBFormat control block — disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt control wordINTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                          | EPROM  | Erasable programmable read-only memory         |

| FCBFormat control block – disk I/O data structureGDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt control wordINTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobits per secondLDTLocal descriptor tableLDTLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                         | ESDI   | Enhanced small device interface                |

| GDTGlobal descriptor tablehHexadecimalICWInterrupt control wordINTInterrupt control wordINTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                      | ETB    | End of transmission block                      |

| hHexadecimalICWInterrupt control wordINTInterrupt control wordINTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                         | FCB    | Format control block - disk I/O data structure |

| ICWInterrupt control wordINTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDRLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                      | GDT    | Global descriptor table                        |

| INTInterruptI/OInput/OutputIRQInterrupt request line or Interrupt requestIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                       | h      | Hexadecimal                                    |

| I/OInput/OutputIRQInterrupt request line or Interrupt requestIRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                       | ICW    | Interrupt control word                         |

| IRQInterrupt request line or Interrupt requestIRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                | INT    | Interrupt                                      |

| IRETReturn from an interruptISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I/O    | Input/Output                                   |

| ISAIndustry standard architectureISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IRQ    | Interrupt request line or Interrupt request    |

| ISRInterrupt service routineISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IRET   | Return from an interrupt                       |

| ISRInterrupt status registerKKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ISA    | Industry standard architecture                 |

| KKilobytesKbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ISR    | Interrupt service routine                      |

| KbsKilobits per secondLDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ISR    | Interrupt status register                      |

| LDTLocal descriptor tableLDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | К      | Kilobytes                                      |

| LDTRLocal descriptor table registerLEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Kbs    | Kilobits per second                            |

| LEDLight-emitting diodeLIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LDT    | Local descriptor table                         |

| LIDLogical IDLSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LDTR   | Local descriptor table register                |

| LSBLeast significant byte (or bit)LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LED    | Light-emitting diode                           |

| LSILarge scale integrationM, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LID    | Logical ID                                     |

| M, MBMegabytesMDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LSB    | Least significant byte (or bit)                |

| MDAMonochrome display adapterMFMModified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LSI    | Large scale integration                        |

| MFM Modified frequency modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | M, MB  | Megabytes                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MDA    | Monochrome display adapter                     |

| MHz Megahertz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MFM    | Modified frequency modulation                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MHz    | Megahertz                                      |

# Acronyms and Abbreviations, Continued

| MMU     | Memory management unit                                  |

|---------|---------------------------------------------------------|

| MSB     | Most significant byte (or bit)                          |

| NCB     | Network control block                                   |

| NMI     | Nonmaskable interrupt                                   |

| OCW     | Operation control word                                  |

| OS/2    | Operating System/2                                      |

| PC      | Personal computer                                       |

| PCLK    | Peripheral clock                                        |

| PEL     | Picture element (pixel)                                 |

| PGA     | Professional graphics adapter                           |

| PIC     | Programmable interrupt controller                       |

| PIO     | Programmed input/output                                 |

| PIT     | Programmable interrupt timer                            |

| POR     | Power-on reset                                          |

| POST    | Power-on self test                                      |

| PTL     | Phoenix Technologies Ltd.                               |

| RAM     | Random access memory                                    |

| RAS     | Row address strobe                                      |

| RGB     | Red-Green-Blue (type of color generator)                |

| RI      | Ring indicator                                          |

| RLL     | Run length limited                                      |

| ROM     | Read-only memory                                        |

| RS-232C | Recommended standard-232C (serial controller interface) |

| RTC     | Real time clock                                         |

| RTS     | Request to send                                         |

| SCSI    | Small computer systems interface                        |

| SDLC    | Synchronous data link communications                    |

| SIMM    | Single inline memory module                             |

| SIP     | Single inline package                                   |

| SMD     | Surface-mount device                                    |

| SSB     | Sense summary block — a disk I/O structure              |

| TSS     | Task state segment                                      |

| TTL     | Transistor-to-transistor logic                          |

|         |                                                         |

# Acronyms and Abbreviations, Continued

| UART | Universal asynchronous receiver/transmitter |

|------|---------------------------------------------|

| VGA  | Video graphics array                        |

| VLSI | Very large scale integration                |

| ХТ   | Extended technology                         |

|      |                                             |

# Chapter 1 The ROM BIOS

### **Overview**

### What is a BIOS?

A basic input output system (BIOS) is the lowest level software component of a computer's operating system. In personal computer systems, the BIOS usually consists of a routine designed to test system hardware and bootstrap load the operating system and a group of device drivers that service system I/O components, such as the keyboard, the display, fixed disk drive, diskette drives, real time clock, parallel ports, serial ports, and other components.

### Two methods for implementing BIOS

There are two methods for implementing a BIOS. The BIOS can be incorporated directly into system software and delivered on diskette as an integral part of the operating system. Or, the BIOS can be tied directly to the system hardware, programmed into ROM on the motherboard or on an expansion card.

### Advantage of the ROM BIOS

As long as the interface between the operating system and the BIOS is standardized, programming the BIOS into ROM has the advantage of allowing system hardware to evolve independently from the operating system. When the BIOS is tied directly to the operating system, however, the operating system must be modified each time there is a change in system hardware.

### PC ROM BIOS

The original IBM PC, a system based on the the 8/16-bit Intel 8088 microprocessor, was introduced in 1981. The IBM PC/XT, a fixed disk capable version of the PC, was introduced in 1983. The IBM PC/AT, a 16-bit system based on the Intel 80286 microprocessor, was introduced in 1984. Clone manufacturers have added Intel 80386-based AT-compatible systems. The BIOSs for all these systems are compatible, in the sense that the later AT BIOSs support all PC and XT BIOS functions in some way.

The BIOS in all models and versions of the IBM PC/XT/AT family of personal computers is programmed into ROM contained on the motherboard. The video BIOSs supporting the EGA and VGA PC video adapters are an exception to this rule. The EGA and VGA BIOSs are programmed into ROM contained on EGA and VGA adapter cards.

### DOS: the PC operating system

PC-DOS, or MS-DOS — its Microsoft Corporation counterpart, is a singletasking operating system capable of addressing the 1 megabyte real mode address range of IBM PC/XT/AT systems. Introduced along with the original IBM PC in 1981, PC-DOS/MS-DOS has emerged as the predominant PC operating system. Both PC- and MS-DOS interface with the ROM BIOS instead of directly with system hardware. Programs that interface with DOS services or directly with the BIOS are assured the highest degree of hardware independence.

### OS/2 and the ROM BIOS

In 1987, IBM introduced OS/2, a multitasking operating system designed for 16-bit PCs. When implemented on IBM PS/2 systems, OS/2 interfaces with the ABIOS portion of the PS/2 ROM BIOS. Although OS/2 can operate on AT class machines, it does not interface with the AT ROM BIOS. There is no BIOS support for OS/2 on an AT, so the level of support usually provided by the BIOS must be built into OS/2. Since OS/2 on an AT must interface directly with the computer hardware, there is a minimal level of portability from system to system with the AT version of OS/2.

**Reference:** For more information on the ABIOS, see ABIOS for IBM PS/2 Computers and Compatibles in this series.

### Terminology used in this book

With the introduction of IBM PC/XT/AT compatible hardware and of IBM PC/XT/AT compatible ROM BIOSs (such as the Phoenix Technologies Ltd. 80x86 ROM BIOSs) came an entire PC "clone" industry. Like their IBM counterparts, the clones also contained a system board ROM BIOS.

Because of their sheer number, keeping track of PC clone model names can be confusing. In this book, "PC" refers to the IBM Personal Computer and compatible systems; "PC/XT" refers to the IBM Personal Computer/XT and compatibles, and "PC/AT" refers to the IBM Personal Computer/AT and compatibles. The terms PC BIOS, XT BIOS, and AT BIOS correspond to the ROM BIOS contained in each of those systems and their compatibles.

### What this chapter is about

This chapter presents a general introduction to the concepts and design features of the IBM PC/XT/AT and compatible ROM BIOS.

The following topics are discussed:

- BIOS: Theory of Operation

- BIOS Memory Usage

- Interrupt Vector Table

- Unexpected Interrupt Handler

- System BIOS Functions and BIOS Diversity

- Summary: The BIOS Services

### **BIOS: Theory of Operation**

### Background

All IBM PC/XT/AT and compatible computer systems are based on the Intel 80x86 or compatible microprocessors. To understand the BIOS architecture, one must consider the interrupt-driven nature of the Intel 80x86 architecture.

In Intel 80x86-based systems, interrupts can be generated by the microprocessor, by system hardware, or by software.

When an interrupt occurs, control of the computer is transferred to an interrupt handling routine. Once the routine has executed, the processor's program counter and flag register are returned to their previous state.

### Where the ROM BIOS fits in